[ad_1]

At the event together we advance_data centers AMD officially presented the fourth generation of EPYC processorsalso known by the code name “Genoa” and based on thearchitecture Zen 4 already used on the Ryzen 7000 series. There are multiple changes compared to the third generation, starting from the maximum number of cores which reaches 96. Support for DDR5 memories and PCIe Gen 5 and CXL 1.1+ standards is also integrated.

4th Generation AMD EPYC: up to 96 cores, DDR5 and PCIe Gen 5

The announcement of the 4th generation AMD EPYC processors does not include particularly surprising elements and aligns with expectations on almost all fronts. In fact, support for DDR5 and PCIe Gen 5 was foreseen, as well as that for the CXL 1.1+ standard (which had been talked about just a few weeks ago).

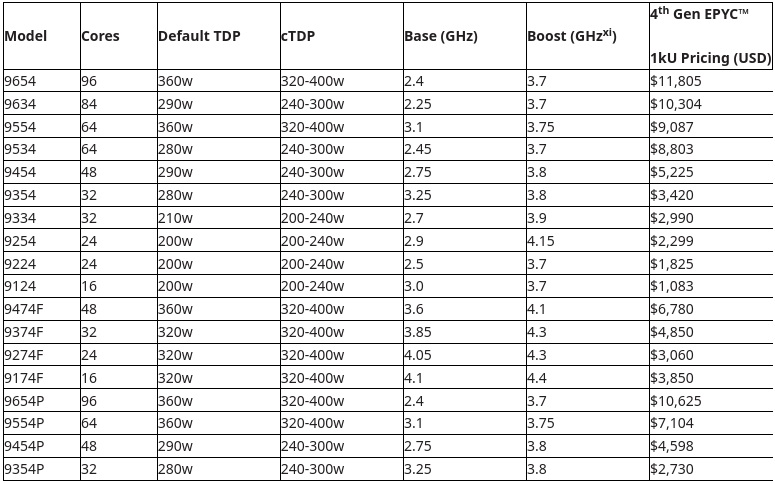

Perhaps the greatest novelty is that the maximum number of cores of the new EPYCs reaches 96 (with 192 threads), against instead the 64 (128 threads) of the previous generation (with an increase, therefore, of 50%). There will be up to 12 CCDs, each with 8 cores. interesting to note how the consumption of the new CPUs remain substantially in line with those of the previous generation, i.e. within the limit of 400 W; the EPYC 9654 model with 96 cores has a TDP equal to 360Wwhich translates to just 3.75W for each core. AMD claims 48% better efficiency than Intel’s competing processors.

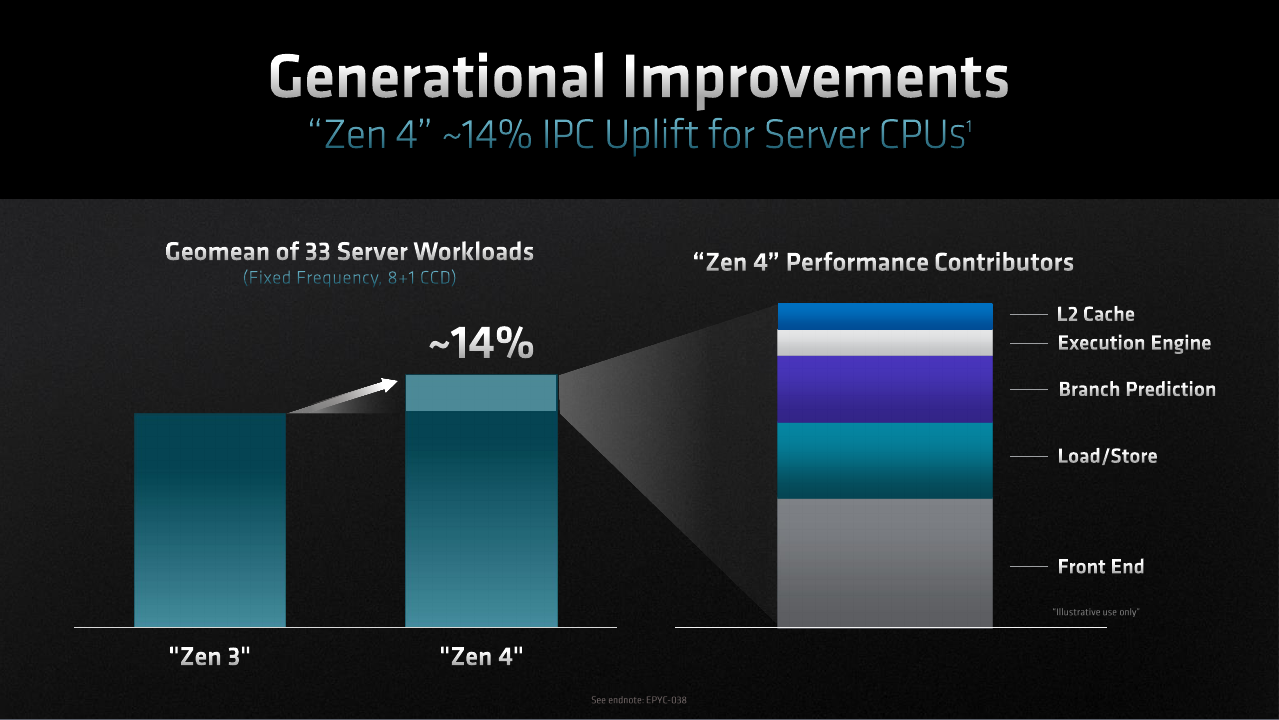

The CCDs are identical to those already seen on Ryzen 7000 for desktop computers, with 8 cores with 1 MB of L2 cache each and 32 MB of shared L3 cache. According to AMD, performance is 14% higher compared to Zen 3 CPUs at the same clock speed. This leap forward is due to improvements in the front-end and load/store units, as well as the branch predictor, the presence of a larger L2 cache and the execution engine.

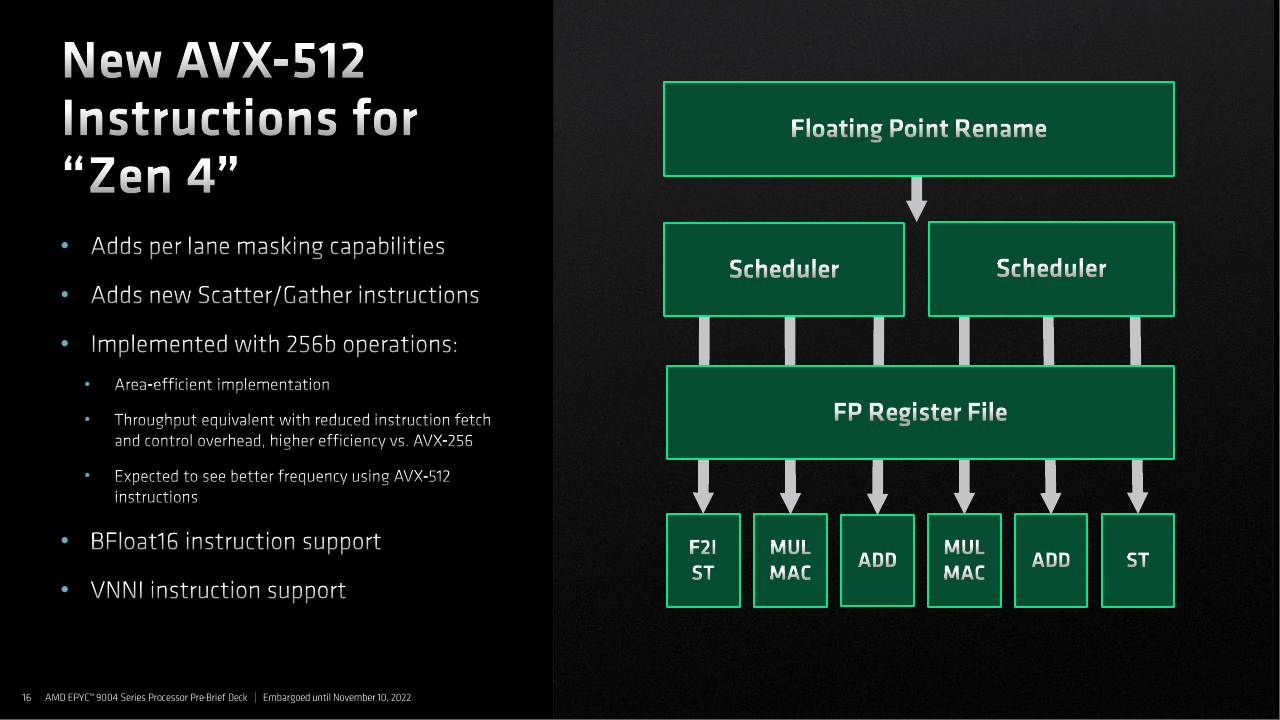

There are also important changes in the ISA, which sees the addition of AVX-512 instructions, VNNI and bfloat16. The AVX-512 implementation, according to AMD, is more efficient than the one used on Intel CPUs, because it uses existing 256-bit FPUs in what AMD calls “double-pumped” mode; We seem to imply that AMD’s AVX-512 instructions require two clock cycles to be computed, rather than just one. VNNI instructions and bfloat16 are used in deep learning and offer better deep learning efficiency than the alternatives.

Improvements are then introduced in the security features, in particular regarding the features of protection of virtual machines. These can choose to run only when there are no other processes running on the same physical core via the second thread; this increases security against attacks that exploit the SMT characteristics of the processors.

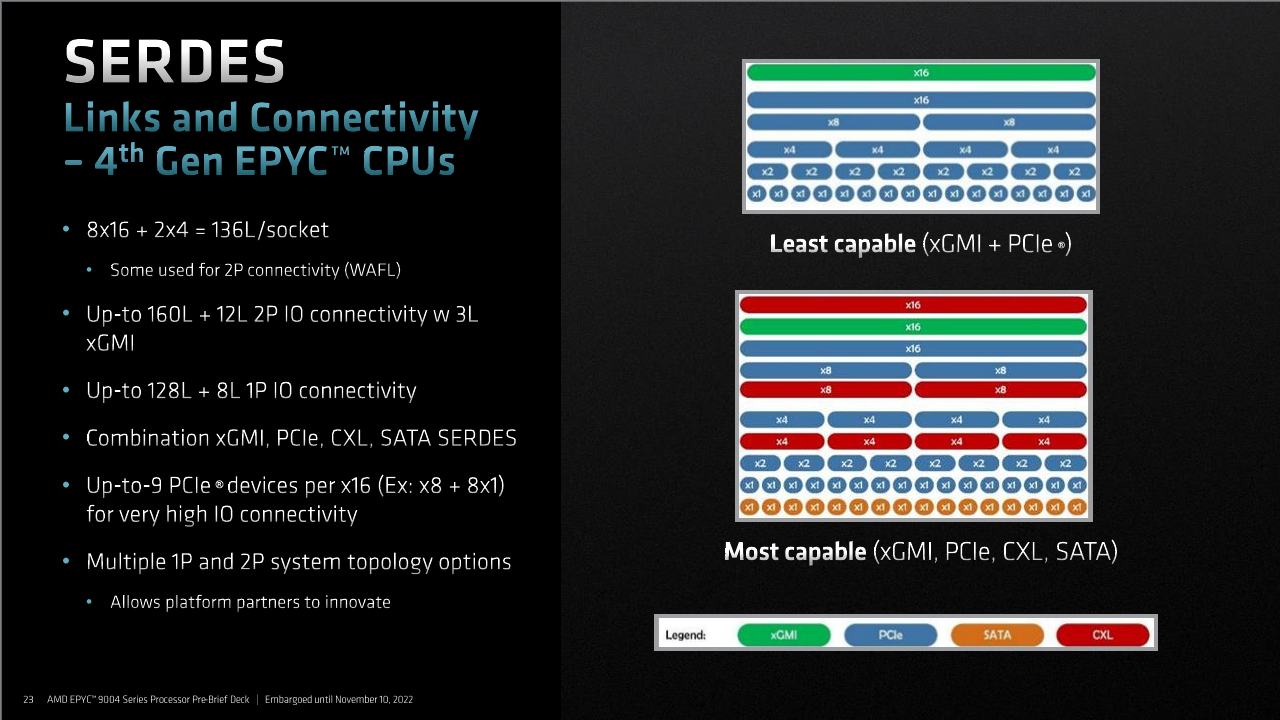

CCDs are produced with 5 nm process, while the Server I/O Die (sIOD) manufactured at 6 nm. The latter has a much higher number of transistors than the previous generation, mainly due to the presence of two SERDES (serializer-deserializer) to 80 lines: Can be configured to handle PCIe Gen 5, CXL 1.1, SATA 6 Gbps or Infinity Fabric channels (for dual processor servers). Speaking of connectivity, the processor supports up to 64 CXL lines And 160 PCIe Gen 5 lanes (that is, up to 10 x16 slots operating at full speed). The third generation Infinity Fabric connects different components within the sIOD, the latter to the CCDs and two CPUs to each other in two-socket servers. The memory interface supports 12 channels (24 40-bit sub-channels) with a up to 6TB of DDR5-4800 ECC memory for each socket.

There are a total of 18 processor models presented by AMD, from 16 up to 96 cores. There are “F” variants that offer fewer cores, but higher frequencies (and, consequently, power consumption).

AMD also announced that EPYC “Bergamo” CPUs, aimed at hyperscalers, will be available in the first half of 2023together with the “Genoa-X” equipped with 3D V-Cache, while the “Siena”, intended for the edge and telecommunications, will be made available in the second half of next year.

.

[ad_2]

Source link